Contents lists available at ScienceDirect

**Microelectronics Journal**

journal homepage: www.elsevier.com/locate/mejo

# Substrate BOX engineering to mitigate the self-heating induced degradation in nanosheet transistor

Sunil Rathore, Rajeewa Kumar Jaisawal, Navneet Gandhi, P.N. Kondekar, Navjeet Bagga

VLSI Design and Nano-scale Computational Lab, Electronics and Communication Engineering Department, PDPM-IIITDM Jabalpur, 482005, India

#### ARTICLE INFO

Keywords:

Nanosheet transistor

Ambient temperature

Thermal contact resistance

Coupled thermodynamic

Self-heating effect

Hydrodynamic

# ABSTRACT

The continued scaling of *3D* transistors into the ultra-scaled-down nanoscale regime causes self-heating effect (SHE) driven thermal deterioration. Particularly in silicon-on-insulator (SOI) FETs, the induced thermal degradation is more severe due to the presence of a conventional lower thermal conductivity material (i.e., SiO<sub>2</sub>) as a buried oxide (BOX), which obstruct the heat flow from the active area to substrate. Thus, the lattice temperature rises above the ambient temperature. Therefore, in this paper, we proposed a substrate-BOX engineered Nanosheet (BOXNS) FET to mitigate the self-heating-induced thermal degradation. Through well-calibrated TCAD models, we investigated the impact of incorporating a superior dielectric material with significantly higher thermal conductivity, such as crystalline diamond ( $k_{th} = 2000 \text{ W m}^{-1} \text{ K}^{-1}$ ) in place of conventional SiO<sub>2</sub>, possessing lower thermal conductivity ( $k_{th} = 1.4 \text{ W m}^{-1} \text{ K}^{-1}$ ) beneath the source and drain region. The results reveal that the proposed BOXNS FET effectively improves the SHE-induced thermal degradation in terms of ON current ( $I_{ON}$ ), OFF current ( $I_{OFF}$ ), effective thermal resistance ( $R_{eff}$ ), and lattice temperature ( $T_{lattice}$ ), compared to the conventional SiO<sub>2</sub> Nanosheet (SiONS) FET. In BOXNS, the hotspots from the active (channel) region find a pathway through the realized crystalline diamond (DLC) and thus decreases the lattice temperature by 13.5 K. Moreover, the dimensional variation, such as channel thickness variation in the proposed BOXNS FET, shows less effective thermal resistance and lattice temperature by 13.5 K.

## 1. Introduction

Over the last two decades, nonplanar device architectures have been widely explored, as conventional planar devices are driven by the severity of the short channel effects (SCEs) [1-3]. The nonplanar multigate devices, such as FinFETs, gate-all-around FETs (GAAFETs), nanowires (NW), etc., provide superior gate control and enhanced performances. A new edition to this era is vertically stacked Nanosheet FETs, which offer higher drivability at the same footprint area of a FinFET [4-6]. Nanosheets (NS) are being explored continuously to satisfy the pace of Moore's law and beyond for high drive current (I<sub>ON</sub>), excellent current ratio (I<sub>ON</sub>/I<sub>OFF</sub>), power performance, and CMOS compatible fabrication flow, and suppressed SCEs compared to the conventional planar MOSFET [7-9]. Nanosheets with fully (partially) bottom dielectric isolation could be a potential candidate primarily due to subsiding leakage current, decreased parasitic capacitance, enhanced frequency response, immunity against process variation, and power performance optimization [10-12]. Despite the excellent gate electrostatics property, the nanosheets suffer from a severe heat-flux crowding issue due to the confined geometry. In nanosheet FET, the sheets (channels) are surrounded by the low thermal conductivity material that creates abysmal self-heating-induced deterioration. The accumulation of heat

and strong phonon confinement severely affects the thermal reliability of the nanosheet FET [13,14]. The severity of the arduous self-heating effects (SHEs) induced thermal degradation is especially more viable in partially bottom dielectric silicon-on-insulator (SOI) nanosheet, which is devised on a conventional buried oxide layer (i.e., SiO<sub>2</sub>). The substrate with SiO<sub>2</sub> as a buried oxide (BOX) obstructs the heat flow from the active sheet area to the substrate due to the presence of lower thermal conductivity material, i.e., SiO<sub>2</sub> ( $k_{th} = 1.4 \text{ W m}^{-1} \text{ K}^{-1}$ ). Moreover, the sheets (i.e., channels) in the nanosheet transistor are also wrapped by the low thermal conductivity material (i.e., SiO<sub>2</sub> as the gate dielectric interfacial layer), which increases the device's thermal resistance. Thus, due to enhanced phonon boundary scattering (PBS), the lattice temperature increases, leading to SHE and, in turn, device

https://doi.org/10.1016/j.mejo.2022.105590

Received 14 August 2022; Received in revised form 16 September 2022; Accepted 18 September 2022 Available online 23 September 2022 0026-2692/© 2022 Elsevier Ltd. All rights reserved.

<sup>\*</sup> Corresponding author. *E-mail address:* navjeet@iiitdmj.ac.in (N. Bagga).

characteristics and reliability severely affected [15]. Consequently, the self-heated lattice temperature reduces threshold voltage's transverse effect and carrier mobility degradation [16,17]. Therefore, SOI-based nanosheet structure doubly deteriorates the device performance, one due to the low thermal conductivity of the SiO<sub>2</sub> and the second because SHE-induced thermal degradation. Thus, we proposed a new structure, i. e., BOXNS FET, which comprises the crystalline diamond (DLC) as the alternative to the SOI concept (i.e., SiONS), in which the thermal insulator SiO<sub>2</sub> is replaced with the attractive diamond insulator material which is an excellent thermal conductor.

Available literature also claimed that the fabrication of DLC as a substrate is compatible with the silicon device fabrication process and could stand without degradation and cross-contamination [18–20]. Crystalline-diamond (DLC) has advantages of having higher thermal conductivity ( $k_{th} = 20 \text{ W cm}^{-1} \text{ K}^{-1}$ ), high electric field breakdown (10 MV cm<sup>-1</sup>), and low dielectric constant ( $\varepsilon_r = 5.7$ ) compared to other dielectric materials [21]. Thus, we proposed a fabrication-compatible BOXNS FET for reliable operation. *The key contributions are*:

- (i) Proposal and investigation of a novel substrate buried oxide (BOX) engineered Nanosheet structure to mitigate the selfheating induced thermal degradation.

- (ii) The results of the proposed BOXNS FET are compared with the baseline SiONS FET, i.e., having a conventional SiO<sub>2</sub> layer as a BOX.

- (iii) The impact of varying the ambient temperature from 300 K to 370 K on various device performances has been thoroughly investigated using well-calibrated TCAD models.

- (iv) The analysis of device dimensional variation, such as channel (sheet) thickness on SHE-induced thermal and electrical performance, has been performed.

The manuscript is organized as follows: Section 2 illustrates the device structure of the baseline (SiONS) and the proposed (BOXNS) FET and calibration setup against the experimental data. The self-heating effect in the proposed BOXNS and SiONS FET are discussed in Section 3, considering the varying ambient temperature and channel thickness. Finally, section 4 concludes the manuscript.

# 2. Device structure and simulation methodology

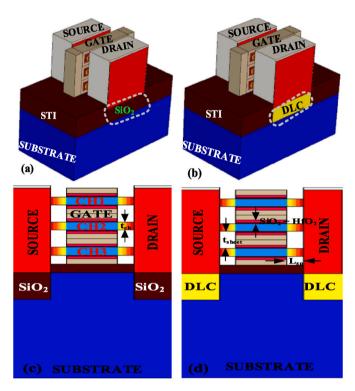

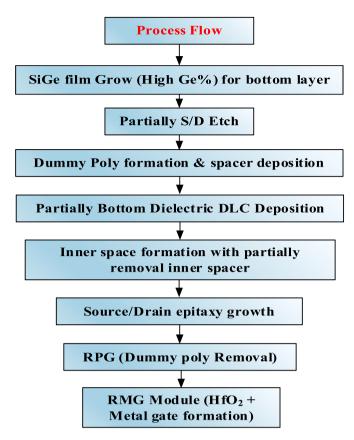

This section explains the device architecture and possible fabrication flow of the proposed BOXNS FET structure. In the proposed BOXNS FET, a diamond-like carbon (DLC) layer is placed beneath the source/drain (S/D) pads, as shown in Fig. 1 (b,d). We have performed an extensive TCAD simulation to analyze the impact of DLC on the device characteristics. The results are also compared with the conventional SiO<sub>2</sub>based SiONS FET, as shown in Fig. 1 (a,c). The S/D and the channel regions are uniformly doped, whereas the Gaussian doping is considered in the extension region to mimic the actual doping scenario. This prevents random dopant fluctuation (RDF), drain-induced barrier lowering (DIBL), and abrupt electric field breakdown [22]. The sheets (channels) are wrapped with dielectric material consisting of 0.9 nm as an effective oxide-thickness (EOT), which comprises SiO<sub>2</sub> as an interfacial layer (IL) of 0.6 nm thickness stacked with 1.7 nm high-k dielectric (i.e., HfO<sub>2</sub>) [23]. In Nanosheet FET (NSFET), the sheets are vertically stacked between S/D pads; thus, the effective heat-flux path would be through the drain pad to the substrate. In the proposed BOXNS FET, the presence of DLC beneath the drain provides a pathway to heat-flux and mitigates the lattice heating. The device parameters used in our simulation are mentioned in Table 1, which are as per International Roadmap for Devices and System (IRDS) projections [24]. In Fig. 2, we have also provided the possible fabrication steps of the proposed BOXNS FET structure using a flow chart. The partially bottom dielectric isolation nanosheet FET is similar to the conventional NSFET and is compatible with the FinFET fabrication technique [12]. The stacked Si/SiGe epitaxy

Table 1 Parameter table.

| Device Parameter                     | Value                             |

|--------------------------------------|-----------------------------------|

| Channel Thickness (t <sub>CH</sub> ) | 4 nm–7 nm                         |

| Channel Width (tw)                   | 25–58 nm                          |

| Channel Length (L <sub>G</sub> )     | 12 nm                             |

| Spacer Length (L <sub>sp</sub> )     | 5 nm                              |

| Interfacial EOT (T <sub>EOT</sub> )  | 0.9                               |

| Spacer Dielectric (k)                | 7.5                               |

| Sheet Spacing (T <sub>sheet</sub> )  | 11 nm                             |

| Source/Drain Doping                  | $2\times 10^{20}~\text{cm}^{-3}$  |

| Channel Doping                       | $1	imes 10^{16}~\mathrm{cm}^{-3}$ |

| Substrate Doping                     | $1	imes 10^{18}~cm^{-3}$          |

| S/D Metal-Si Interface Resistance    | $8.4	imes10^{-10}\Omega cm^2$     |

**Fig. 1.** (a–b) 3D schematic of the buried  $SiO_2$  Nanosheet (SiONS) FET and buried DLC BOXNS FET beneath the source/drain region; (c) 2D cross-sectional structure for fair comparison of vertically stacked nanosheet transistor with  $SiO_2$  as a buried oxide layer beneath S/D pads; (d) 2D cross-sectional view of the proposed vertically stacked BOXNS FET comprises DLC instead of SiO<sub>2</sub>. The crystalline diamond (DLC) is strategically placed under the source/drain (S/D) region to subside the leakage current and SHE.

layer is grown as the first layer containing a high percentage of Ge layer. The ultra-high selectivity process is required to prevent erosion during the channel release, followed by the inner and outer spacer formation [12]. The bottom dielectric layer below S/D plays a vital role because this region is exposed to multiple etch processes. Here, crystalline diamond (DLC) having higher thermal conductivity is strategically placed beneath the S/D pads in the BOXNS FET to mitigate the SHE-induced thermal degradation [25], which acts as the thermal dielectric and provides the heat removal path. Replacing the partially bottom SiO<sub>2</sub> with the crystalline diamond is a practical step as it is compatible with the current integrated circuit fabrication technology [26]. The remote roughness scattering can be reduced by utilizing various bonding approaches [27]. Si<sub>3</sub>N<sub>4</sub> is used as the spacer to assuage the gate-source/drain fringing capacitance, and TiN is used as a gate electrode.

**Fig. 2.** The possible fabrication flow of the partial bottom Silicon on diamond nanosheet (BOXNS) FET and partially bottom Silicon on insulator (SiONS) nanosheet transistor.

#### • TCAD Calibration:

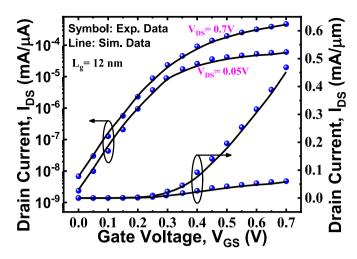

A vertically stacked nanosheet with substrate engineered BOX layer, i.e., BOXNS FET, is realized using Sentaurus TCAD [28]. The models employed in the TCAD setup are well-tuned and calibrated against the experimental data [7]. The density gradient model is invoked to capture the channel.

spatial and electrostatic quantum confinement. To capture the carrier distribution near the oxide/silicon interface, the modified local density approximation model (MLDA) is included. Further, the ballistic, vertical field, and high field saturation models are incorporated to consider the impact of short channel effects (SCEs) [29]. The inversion and accumulation layer (IAL) mobility models have been included to assess the mobility deterioration caused by surface roughness scattering, phonon scattering, and Coulomb scattering. The Slotboom model was employed to capture the doping/temperature-dependent bandgap narrowing. The Shockley-Read-Hall (SRH) model is used to study the cumulative effect of carrier generation and recombination. Finally, the work function of the TiN is tuned to the permissible limit to match the simulated and experimental transfer characteristics (I<sub>DS</sub>-V<sub>GS</sub>), as shown in Fig. 3. In general, the thermal conductivity  $(k_{th})$  of the channel is decreased due to surface phonon scattering [30]. The thermal conductivity (kth) of the Silicon depends on the lattice temperature (Tlattice), channel thickness (t<sub>CH</sub>), doping (N<sub>d</sub>), and the mole fraction (x), as follows [31]:

$$k = \frac{1}{3} \times \frac{1}{2\pi^{x}} \times n_{j} \times \sum_{j} \int_{0}^{\omega_{0,j}} \frac{\tau_{\omega,j}}{\nu_{\omega,j}} C(\omega) \omega^{2} d\omega$$

<sup>(1)</sup>

$$C(x) = kx^2 e^x (e^x - 1)^{-2}$$

(2)

Fig. 3. TCAD Calibration against the experimental data [7], showing a good match in  $I_{DS}$ - $V_{GS}$  (transfer characteristics) data.

$$=\hbar\omega_{/kT}$$

(3)

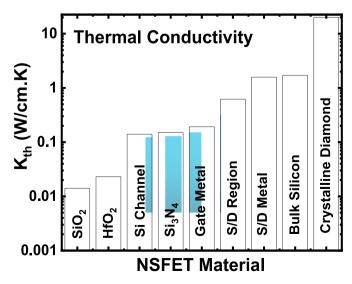

Here,  $\nu_{\omega_j}$  and  $\omega_{0j}$  denotes the velocity and maximum frequency, respectively.  $\tau_{0,j}$  represents the total relaxation time. In our simulation, the interface thermal contact resistance is considered as  $4 \times 10^{-5} \text{ cm}^2 \text{K}/\text{W}$  [32–35]. Fig. 4 shows a comparative bar chart of the thermal conductivities of different materials used in our simulation. Not to mention otherwise, in our TCAD simulation, drift-diffusion along with lattice heat flow equations are used to capture the self-heating effect in the NSFET. The energy balance equations from the hydrodynamic model are used to calculate the heat flux.

## 3. Results and discussion

*x* =

In this section, we discuss the self-heating-induced performance evaluation and the impact of ambient temperature on the device characteristics of the SiONS and BOXNS FET. The impact of the device geometry variation is also investigated. The section is divided into the following sub-sections:

Fig. 4. Shows the thermal conductivity values of the materials used to fabricate nanosheet FET.

# 3.1. Device performance evaluation under SHE

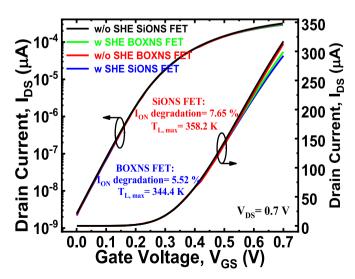

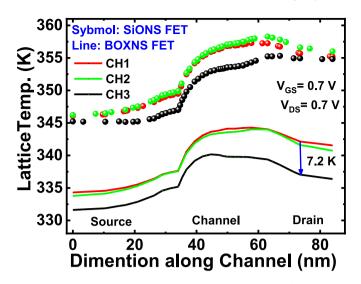

This subsection deals with the electrical characteristic of the proposed BOXNS FET and SiONS FET under the consideration of the selfheating effect (SHE) induced thermal degradation. The impact of the SHE-induced thermal degradation is evaluated in terms of ON current (ION) degradation of the SiONS FET compared to the BOXNS FET to analyze the severity of the SHE. Fig. 5 shows the impact of the SHE on the transfer characteristics of both the BOXNS and SiONS FET. A small peak (0.8%) current degradation is observed in BOXNS FET due to surface roughness scattering at the silicon-diamond interface [27]. Due to SHE, heat accumulation occurs in the active (channel/sheet) region and degrades the  $I_{\text{ON}}$ , increasing the lattice temperature. Thus, the device performance to its zenith values decreases. We observed that  $I_{\mbox{\scriptsize ON}}$  is degraded by ~7.65%, and lattice temperature is enhanced to 58.2 K at room temperature (300 K) in SiONS FET. However, using the crystalline diamond beneath the S/D pads in the BOXNS FET, the I<sub>ON</sub> is improved by  $\sim$ 2.8%, and the lattice temperature is enhanced to 13.8 K. This is due to the decrease in heat accumulation in the active (channel/sheet) region at the drain side and shifting the heat flow path towards the substrate compared to SiONS FET. Fig. 6 shows the spatial variation of the lattice temperature along the channel direction. The maximum value of the hotspot of lattice temperature is observed at the channel and drain junction. The high-energy electrons move under the influence of a high electric field from the source region scattered heavily with the optical phonons and transfer their joule and carrier energy (kinetic energy) and undergo energy relaxation at the drain side, which results in enhanced lattice temperature. However, the lattice temperature difference between channel-1 (CH1) to channel-3 (CH3) is 7.2 K in BOXNS FET compared to the SiONS FET at the drain side due to heat energy dissipated towards the substrate.

#### 3.2. Impact of ambient temperature on BOXNS and SiONS FET

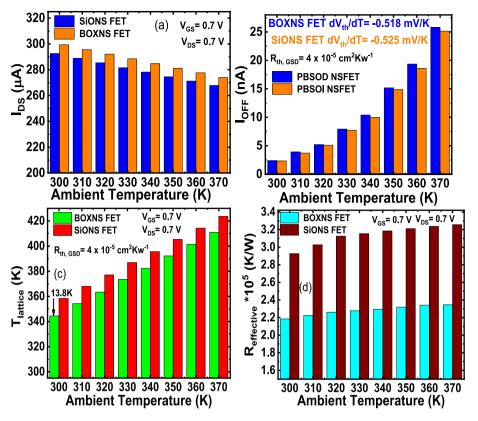

The performance characteristics of electronic devices are significantly affected by ambient temperature. Fig. 7 shows the impact of varying the temperature on the electrical (I<sub>ON</sub> and I<sub>OFF</sub>) and thermal characteristics (T<sub>lattice</sub> and R<sub>effective</sub>) of the BOXNS and SiONS FET, respectively. As the temperature increases from room temperature to 370 K, the lattice temperature (T<sub>lattice</sub>) increases from 358.2 K to 420 K (17.32%) in SiONS FET. Due to this, the effective thermal resistance increases by ~8.47%, which results in ON current degradation from 290  $\mu$ A to 280  $\mu$ A (~8.72%) and 10.4 times enhancement in leakage current.

**Fig. 5.** Shows the transfer characteristics ( $I_{DS}$ - $V_{GS}$ ) of NSFET with partially depleted silicon on the insulator (SiONS) and proposed silicon on the diamond (BOXNS) with and without a self-heating effect.

**Fig. 6.** Shows the variation of the lattice temperature along the channel. While strategically placing the DLC beneath the S/D region, the BOXNS FET lowers the lattice temperature. Also, the difference between the lattice temperature variation in CH1 and CH3 is increased in BOXNS FET due to a change in the effective heat flow path (hotspot) towards the substrate region.

However, using the DLC as a BOX layer in BOXNS FET, the effective heat flux shifted from the device active (channel/sheet) region towards the substrate (Fig. 6), which resulted in 3.83% and 28.12% improvement in  $T_{lattice}$  and  $R_{effective}$ , respectively.

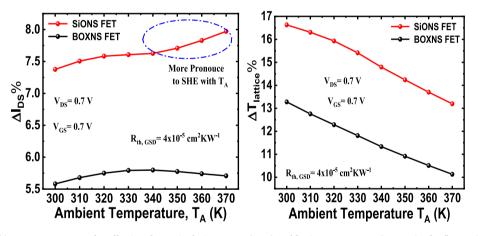

Therefore, the ON current is improved by 2.8% compared to SiONS FET. The variation in ambient temperature severely affects the threshold voltage shift and can be measured by using the  $\Delta V_{th}/\Delta T$  [36]. When ambient temperature increases from 300 K to 370 K, the observed threshold voltage coefficient is -0.525 mV/K for SiONS FET and -0.518 mV/K for BOXNS FET, which proves the higher thermal reliability of the BOXNS FET compared to the SiONS FET. The OFF current in both devices is almost similar (Fig. 7b) due to less scattering occurring in the channel region at lower gate voltage. The effect of SHE-induced degradation is more at higher ambient temperatures in SiONS FET than BOXNS FET, as shown in Fig. 8. At higher temperatures, the thermal conductivity is reduced, resulting in more heat accumulation in the device, and current decreases steadily in SiONS FET. However, using a higher thermal conductivity material releases the accumulated heat towards the substrate; thus, SHE is less pronounced in BOXNS FET. The change in drain current and lattice temperature is calculated as mentioned in Eqs. (4) and (5) [37,38]:

$$\Delta I_{ON} = \frac{I_{L,w/o} \text{ she} - I_{L,w} \text{ she}}{I_{L,w/o} \text{ she}} \times 100 \%$$

(4)

$$\Delta T_{Lattice} = \frac{T_{L,Max} - T_A}{T_{Amb}} \times 100 \%$$

<sup>(5)</sup>

where  $I_{L,\ w\ SHE}$  and  $I_{L,\ w/o\ SHE}$  is the drain current with and without self-heating effect, and  $T_{L,\ Max}$  is maximum lattice temperature with SHE consideration.

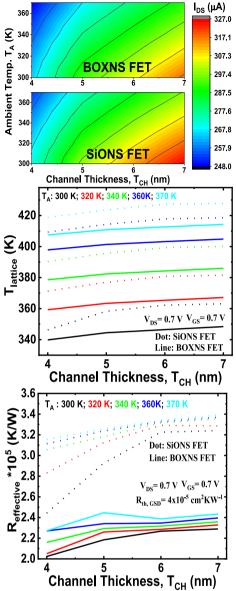

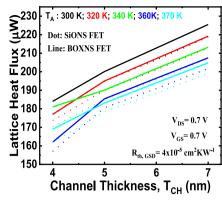

#### 3.3. Impact of channel thickness

The variation in device geometry significantly affects the electrical and thermal characteristics due to the change in gate controllability and mobility of the device. Therefore, the impact of varying the channel thickness ( $T_{CH}$ ) while varying the ambient temperature of the NSFET is necessary to get a deeper detailed insight into the self-heating effect-induced thermal degradation. Fig. 9 shows the variation in  $T_{CH}$  from 4 nm to 7 nm and its impact on the parameters such as lattice temperature, effective thermal resistance, and lattice heat flux. However, by

Fig. 7. Shows the impact of varying the temperature on device electrical (I<sub>ON</sub> and I<sub>OFF</sub>) and thermal characteristics (T<sub>lattice</sub> and R<sub>effective</sub>) of SiONS and BOXNS FET.

Fig. 8. The impact of ambient temperature on the effective change in drain current ( $\Delta I_{DS}$ ) and lattice temperature ( $\Delta T_{lattice}$ ). The fluctuation in  $\Delta I_{DS}$  and  $\Delta T_{lattice}$  is less pronounced in BOXNS FET due to the uniform distribution of lattice temperature.

increasing the channel thickness increases the surface-to-volume ratio, which increases the inversion charge density and causes an increase in the drain current. Moreover, the increase in ambient temperature reduces carrier mobility, which results in a decrease in drain current.

However, this  $I_{ON}$  degradation can be mitigated using BOXNS FET (Fig. 9a). With an increase in  $T_{CH}$ . In the BOXNS structure with increasing  $T_{CH}$ , the primary heat dissipation path increases, which increases the lattice heat flux (Fig. 9b) and lattice temperature of the device (Fig. 9c). Increasing the channel thickness enhances the circumference of the device; however, the thermal heat conductivity of the device stagnates, suggesting that higher channel thickness prevents the continuous enhancement of the lattice temperature and effective thermal resistance; thus, improved thermal reliability of the device is obtained. However, due to the use of crystalline diamond, the primary

heat path in SiONS FET is altered from the device active (channel/sheet) region towards the substrate in BOXNS FET. Thus, the acquired results show that proper consideration of device dimension and substrate material can mitigate the self-heating effect in Nanosheet FET.

# 4. Conclusions

Using well-calibrated TCAD models, we have proposed a new BOXNS FET comprising the crystalline diamond beneath the drain and source regions, helping to mitigate the self-heating-induced thermal degradation. We evaluated the performance of the proposed BOXNS FET in comparison to the conventional SiO<sub>2</sub> layer-based NSFET, i.e., SiONS FET. The crystalline diamond having a heat thermal conductivity (~1000 times higher than SiO<sub>2</sub>) is employed, which leads to the removal

S. Rathore et al.

Fig. 9. Impact of increasing the channel thickness and ambient temperature on (a) drain current variation in contour plot, (b) lattice heat flux, (c) lattice temperature, and (d) effective thermal resistance. Steadily increasing the channel thickness of the NSFET enhance the lattice heat flux, which enhances the lattice temperature and effective thermal resistance of the device. However, the drain current of the device increases due to enhancement in inversion charge particles with the enhanced surface-to-volume ratio.

of the hotspot towards the substrate. Thus, it enhances the heat removal capability and allows the uniform distribution of the lattice temperature in the device's active (channel) regions. Therefore, by increasing the ambient temperature from 300 K to 370 K, the average rise in the device lattice temperature is improved by 13.8 K, and device thermal resistance is decreased by 28.12%. This results in approximately  $\sim 2.8\%$ improvement in the ION in BOXNS FET compared to SiONS FET. Further, we have also investigated the impact of varying channel thickness on device performance. As the sheet thickness increases from 4 nm to 7 nm, the surface-to-volume ratio increases the heat dissipation path, which enhances the lattice temperature, lattice heat flux, and effective thermal resistance. However, due to the use of crystalline diamond, the severity of SHE-induced thermal degradation is less affected, and lattice temperature, lattice heat flux, and effective thermal resistance are improved by 25.8%, 42%, and 50.2% in BOXNS FET compared to SiONS FET. Therefore, the proposed BOXNS FET can be a promising candidate for high-volume production and energy-efficient future FET devices due to overcoming the power accumulation constraints in electronics.

#### Author statement

Sunil Rathore: Conceptualization, Methodology, Data curation, Software, Writing – original draft preparation, Investigation. Rajeewa Kumar Jaisawal: Conceptualization, Methodology, Investigation, Software. Navneet Gandhi: Conceptualization, Methodology, Investigation. P. N. Kondekar: Supervision, Visualization. Navjeet Bagga: Supervision, Writing- Reviewing and Editing, Corresponding Author, Conceptualization, Visualization.

#### Declaration of competing interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

# Data availability

The data that has been used is confidential.

#### Acknowledgment

N. Bagga greatly acknowledged the support received from the PDPM IIITDM Jabalpur, project title "Design and Performance Investigation of Negative Capacitance Tunnel Field Effect Transistor for Digital/Analog Applications," project no.IIITDMJ/ODRSPC/2022/88.

#### References

- [1] D. Nagy, G. Indalecio, A.J. Garcia-Loureiro, M.A. Elmessary, K. Kalna, N. Seoane, FinFET versus gate-all-around nanowire FET: performance, scaling, and variability, IEEE J. Electron Devices Soc. 6 (1) (2018) 332–340, https://doi.org/10.1109/ JEDS.2018.2804383.

- [2] Ankit Dixit, Dip Prakash Samajdar, Navjeet Bagga, Dielectric modulated GaAs1-xSbX FinFET as a label-free biosensor: device proposal and investigation, Semicond. Sci. Technol. 36 (No. 9) (2021) 95033, https://doi.org/10.1088/1361-6641/ac0d97. Aug.

- [3] Navjeet Bagga, Nitanshu Chauhan, Shashank Banchhor, Divyam Gupta,

S. Dasgupta, Demonstration of a novel tunnel FET with channel sandwiched by drain, Semicond. Sci. Technol. 35 (No. 1) (Nov. 2019) 15008, https://doi.org/ 10.1088/1361-6641/ab5434.

- [4] Sresta Valasa1, Shubham Tayal, and Laxman Raju Thoutam, "Design insights into thermal performance of vertically stacked JL-NSFET with high-k gate dielectric for sub 5-nm technology node," ECS J. Solid State ss8777/ac6627.

- [5] V.B. Sreenivasulu, V. Narendar, Circuit analysis and optimization of GAA nanowire FET towards low power and high switching, Silicon (2022), https://doi.org/ 10.1007/s12633-022-01777-6.

- [6] R.K. Jaisawal, P. Kondekar, S. Yadav, P. Upadhyay, B. Awadhiya, S. Rathore, Insights into the operation of negative capacitance FinFET for low power logic applications, Microelectron. J. (Jan. 2022) 105321, https://doi.org/10.1016/j. mejo.2021.105321.

- - R. Muthinti, J. Li, R. Wong, D. Brown, P. Oldiges, R. Robison, J. Arnold, N. Felix, S. Skordas, J. Gaudiello, T. Standaert, H. Jagannathan, D. Corliss, M.-H. Na,

- A. Knorr, T. Wu, D. Gupta, S. Lian, R. Divakaruni, T. Gow, C. Labelle, S. Lee,

- V. Paruchuri, H. Bu, M. Khare, Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET T230 T231, VLSI Technol 5 (1) (2017) 14–15, https://doi.org/10.23919/VLSIT.2017.7998183.

- [8] Rajeewa Kumar Jaisawal, Sunil Rathore, Navneet Gandhi, P.N. Kondekar, Navjeet Bagga, Role of Temperature on Linearity and Analog/RF Performance Merits of a Negative Capacitance FinFET, Aug. 2022, https://doi.org/10.1088/ 1361-6641/ac9250.

- [9] N. Bagga, K. Ni, N. Chauhan, O. Prakash, X.S. Hu, H. Amrouch, Cleaved-gate ferroelectric FET for reliable multi-level cell storage, IEEE International Reliability Physics Symposium (IRPS) (Mar. 2022), https://doi.org/10.1109/ IRPS48227.2022.9764553. P5-1-P5-5.

- [10] V.B. Sreenivasulu, V. Narendar, p-Type trigate junctionless nanosheet MOSFET: analog/RF, linearity, and circuit analysis, ECS J Solids State Sci Technol 10 (2021), 123001, https://doi.org/10.1149/2162-8777/ac3bdf.

- [11] C. Yoo, J. Chang, Y. Seon, H. Kim, J. Jeon, Analysis of self-heating effects in multinanosheet FET considering bottom isolation and package options, in: IEEE Transactions on Electron Devices, vol. 69, March 2022, pp. 1524–1531, https:// doi.org/10.1109/TED.2022.3141327, 3.

- [12] J. Zhang, J. Frougier, A. Greene, X. Niao, L. Yu, R. Vega, P. Montanini, C. Durfee, A. Gaul, S. Pancharatnam, C. Adams, H. Wu, H. Zhou, T. Shen, R. Xie, M. Sankarapandian, J. Wang, K. Watanabe, R. Bao, X. Liu, C. Park, H. Shobha, P. Joseph, D. Kong, A. Arceo De La Pena, J. Li, R. Conti, D. Dechene, N. Loubet, R. Chao, T. Yamashita, R. Robison, V. Basker, K. Zhao, D. Guo, B. Haran, R. Divakaruni, H. Bu, Full bottom dielectric isolation to enable stacked nanosheet transistor for low power and high performance applications, IEEE Int. Electron Devices Meeting (Feb. 2019), https://doi.org/10.1109/ IEDM19573.2019.8993490, 11.6.1-11.611.64.

- [13] S. Venkateswarlu, O. Badami, K. Nayak, Electro-thermal performance boosting in stacked Si gate-all-around nanosheet FET with engineered source/drain contacts, IEEE Trans. Electron. Dev. 68 (9) (Sept. 2021) 4723–4728, https://doi.org/ 10.1109/TED.2021.3095038.

- [14] S. Rathore, R.K. Jaisawal, P.N. Kondekar, N. Bagga, Design optimization of threestacked nanosheet FET from self-heating effects perspective, IEEE Trans. Device Mater. Reliab. 22 (3) (Sept. 2022) 396–402, https://doi.org/10.1109/ TDMR.2022.3181672.

- [15] V. Jegadheesan, K. Sivasankaran, A. Konar, Optimized substrate for improved performance of stacked nanosheet field-effect transistor, IEEE Trans. Electron. Dev. 67 (10) (2020) 4079–4084, Oct, https://doi.org/10.1109/TED.2020.3017175.

- [16] H. Jiang, et al., Experimental investigation of self-heating effect (SHE) in multiplefin SOI FinFETs, Semicond. Sci. Technol. 29 (Sep. 2014) 115021.

- [17] L. Yin, G. Du, X. Liu, Impact of ambient of ambient temperature on the self-heating effects in FinFETs, J. Semiconduct. 39 (Jun 2018), 094011, https://doi.org/ 10.1088/1674-4926/39/9/094011.

- [18] A. Aleksov, J.M. Gobien, X. Li, J.T. Prater, Z. Sitar, Silicon-on-Diamond an engineered substrate for electronic applications, Diam. Relat. Mater.Mar 15 (2006) 248–253, https://doi.org/10.1016/j.diamond.2005.09.012.

- [19] Arash Daghighi, A novel structure to improve DIBL in fully-depleted silicon-ondiamond substrate, Diam. Relat. Mater. 40 (Nov) (2013) 51–55, https://doi.org/ 10.1016/j.diamond.2013.10.010.s.

- [20] Yong Ju Lee, Formation of aluminum nitride thin films as gate dielectrics on Si (100), J. Cryst. Growth 266 (Jun 2004) 568–572, https://doi.org/10.1016/j. jcrysgro.2004.03.016.

- [21] Y.Q. Liu, M.H. Ding, J.J. Su, H. Ren, X.R. Lu, W.Z. Tang, An investigation on dielectric properties of diamond films in the range of K and Ka band, Diam. Relat. Mater. 73 (Mar) (2017) 114–120, https://doi.org/10.1016/j. diamond 2016 08 007

- [22] K. Nayak, S. Agarwal, M. Bajaj, K.V.R.M. Murali, V.R. Rao, Random dopant fluctuation induced variability in undoped channel Si gate all around nanowire n-MOSFET, IEEE Trans. Electron. Dev. 62 (2) (Feb. 2015) 685–688, https://doi.org/ 10.1109/TED.2014.2383352.

- [23] V.B. Sreenivasulu, V. Narendar, Design insights of nanosheet FET and CMOS circuit applications at 5-nm technology node, IEEE Trans. Electron. Dev. 69 (8) (2022) 4115–4122, Aug, https://doi.org/10.1109/TED.2022.3181575.

- [24] International Roadmap for Devices and Systems, 2020 [Online]. Available: https: //irds.ieee.org/editions/2020.

- [25] Jacques Pelletier, André Anders, Plasma-based ion implantation and deposition: a review of physics, technology, and applications, *IEEE Transactions on Plasma Science*, Special Issue on Ion Sources 33 (6) (May 2005).

- [26] P.K. Chu, B.Y. Tang, Principles and Characteristics of a New Generation Plasma Immersion Ion Implanter, 68, Jun. 1998, https://doi.org/10.1063/1.1147959.

- [27] Zengfeng Di, Paul Chu, Zhu, et al., Fabrication of silicon-on-SiO2/diamondlikecarbon dual insulator using ion cutting and mitigation of self-heating effects, Appl. Phys. Lett. 88 (Feb, 2006), https://doi.org/10.1063/1.2192981, 142108-142108.

- [28] Synopsys, Sentaurus Device User Guide, Mountain View CA, Synopsys, Inc., 2020.

- [29] R.K. Jaisawal, S. Rathore, P.N. Kondekar, S. Yadav, B. Awadhiya, P. Upadhyay, N. Bagga, Assessing the analog/RF and linearity performances of FinFET using high threshold voltage techniques, Semiconductors Science and Technology 37 (5) (Apr. 2022), 055010, https://doi.org/10.1088/1361-6641/ac6128.

- [30] M. Asheghi, Katsuo Kurabayashi, R. Kasnavi, Kenneth Goodson, Thermal conduction in doped single-crystal silicon films, J. Appl. Phys. 91 (Apr. 2002) 5079–5088, https://doi.org/10.1063/1.1458057.

- [31] M.G. Holland, Analysis of lattice thermal conductivity, Phys. Rev. 132 (6) (Dec. 1963) 2461–2471, https://doi.org/10.1103/PhysRev.132.2461.

- [32] Ju Liu, Feng Han, Xiaobing Luo, Run Hu, Sheng Liu, A simple setup to test thermal contact resistance between interfaces of two contacted solid materials, in: 2010 International Conference on Electronic Packaging Technology & High Density Packaging, 2010, pp. 116–120, https://doi.org/10.1109/ICEPT.2010.5582472.

- [33] S. Banchhor, N. Chauhan, A Bulusu, A new physical insight into the zerotemperature coefficient with self-heating in silicon-on-insulator fin field-effect transistors, in: Semiconductor Science Technology, vol. 36, IOP, Jan. 2021, p. 035005, https://doi.org/10.1088/1361-6641/abd220.

- [34] K. Jagannadham, Thermal conductivity and interface thermal conductance of titanium silicide films on Si, IEEE Trans. Electron. Dev. 63 (1) (Jan. 2016) 432–438, https://doi.org/10.1109/TED.2015.2501025.sss.

- [35] S. Rathore, R.K. Jaisawal, P. Suryavanshi, P.N. Kondekar, Investigation of ambient temperature and thermal contact resistance induced self-heating effects in nanosheet FET, Semicond. Sci. Technol. 37 (5) (Apr. 2022), 055019, https://doi. org/10.1088/1361-6641/ac62.

- [36] V.B. Sreenivasulu, V. Narendar, Junctionless SOI FinFET with advanced spacer techniques for sub-3 nm technology nodes, AEU - International Journal of Electronics and Communications 145 (2022), https://doi.org/10.1016/j. aeue.2021.154069, 154069.

- [37] J.-Y. Yan, et al., Thermal resistance modeling of back-end interconnect and intrinsic FinFETs, and transient simulation of inverters with capacitive loading effects, in: 2016 IEEE International Electron Devices Meeting (IEDM), 2016, pp. 35.6.1–35.6.4, https://doi.org/10.1109/IEDM.2016.7838550.

- [38] N. Aruna Kumari, P. Prithvi, Device and circuit-level performance comparison of GAA nanosheet FET with varied geometrical parameters, Microelectron. J. 125 (July 2022), 105432, https://doi.org/10.1016/j.mejo.2022.105432.